瑞士的科学家们发明了一种使用极低损耗氮化硅晶圆制造光子集成电路的新方法。研究人员声称,这项技术只需借助传统半导体制造技术,即可实现频率梳及其他非线性器件的量产。(原文见:Nature Communications: doi: 10.1038 / s41467 - 021 - 21973 - z)。

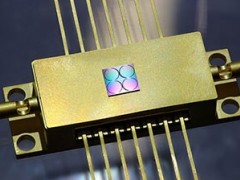

图1 EPFL的研究人员发明了一种基于CMOS的制造工艺,可产生超低损耗的光子微谐振器和一米长的螺旋形波导

微梳(microcomb)及半导体材料

硅材料被誉为是现代电子学的支柱,在集成光子学中发挥了重要作用。目前已经在数据中心互联等形式中被广泛部署。但在制造微型频率梳(即“微梳”)等非线性器件时,硅材料有一定局限性。微梳是一种微小的环形谐振器,能够利用折射率随光强的变化而变化的克尔效应,把一束连续的激光束转换成一串由许多非常窄的等间距频率线组成的短脉冲。

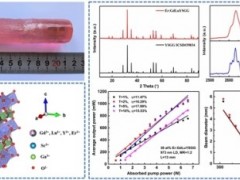

研究人员已经用一系列材料制成了微梳,包括铌酸锂、砷化镓铝、碳化硅和金刚石。氮化硅(Si3N4)兼具光学损耗极低、克尔非线性强和紧凑等优点,是一种非常适用于制作微梳的材料。如果将氮化硅波导制成高度小于100纳米的细长状,其损耗可以低至0.3 dB/m。但这种形状却会限制其克尔非线性。因此,迄今为止,相干通信、激光测距、天文光谱仪校准和光学时钟等多数微梳应用种,使用的都是700纳米以上厚度的波导。

光子镶嵌(Damascene)工艺

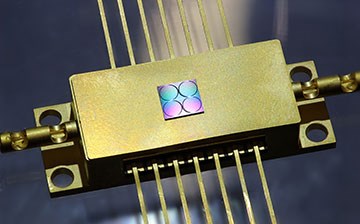

图2 集成氮化硅光子芯片约为5×5 mm2

在最新的工作中,美国光学学会会士Tobias Kippenberg、美国光学学会学生成员Junqiu Liu及其瑞士洛桑联邦理工学院(EPFL)的同事展示了使用标准CMOS制造技术制造950纳米厚的低损耗微梳的方法。其他研究小组广泛使用的是电子束光刻技术,而他们则采用了基于深紫外光刻技术的“光子镶嵌(Damascene)工艺”来提高产量、稳定性和重复性。这一工艺类似于大马士革过去制作装饰品的方式,即先将金属放在模具中,然后对其进行抛光。在这种情况下,首先考虑使用的材料是氮化硅。研究人员首先使用光刻技术,然后进行干法蚀刻和退火,在二氧化硅衬底上精准刻出波导通道;随后在上面沉积一微米厚的氮化硅薄膜,并使用回刻平坦化技术将其表面磨平;然后再进行进一步退火,同时用二氧化硅覆盖电路。

Kippenberg及其同事们制作了几十个4英寸的晶圆,每个晶圆包含超过200个5×5平方毫米的芯片,其中包含不同大小的微谐振器(即不同谱线间距的微梳)。激光光谱学测量谐振器线宽结果显示,其平均品质因数约为3000万。同时还测量了晶圆良率,即品质因数高于1000万的芯片的比例,结果在80%到90%之间。

进一步降低损耗

为了证明这种工艺的确可实现高产量、晶圆规模的制造,瑞士洛桑联邦理工学院的小组还制作了长螺旋形波导(如用于制造延迟线的波导)。研究小组将一米长的螺旋形波导装入了略高于6平方毫米的空间中,比细芯氮化硅波导面积要小300倍。其实现的最低损耗为2.4 dB/m,高于微谐振器的最低损耗(约为1 dB/m),其中部分原因在于晶圆片上的颗粒污染造成的光散射缺陷。

研究人员发现,这种波导的固有损耗主要是瑞利散射,因此,可通过优化光刻和蚀刻工艺进一步减少损耗。在理想条件下可将这些损耗降低到零,即波导只受吸收损耗的限制。在这种情况下,品质因数可达到在2亿左右,相当于0.15 dB/m。

Liu指出,制造完全集成的微梳需要将氮化硅芯片与其他由不同材料(如硅和磷化铟)制成的芯片相结合,以产生激光增益介质。他说,他的团队与加州大学圣巴巴拉分校的另一个团队实际上已经开发了一种基于CMOS的技术,以在硅基上制造这种集成微梳,在4英寸的晶圆上可制造数千个微梳。

客服热线:

客服热线: